- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

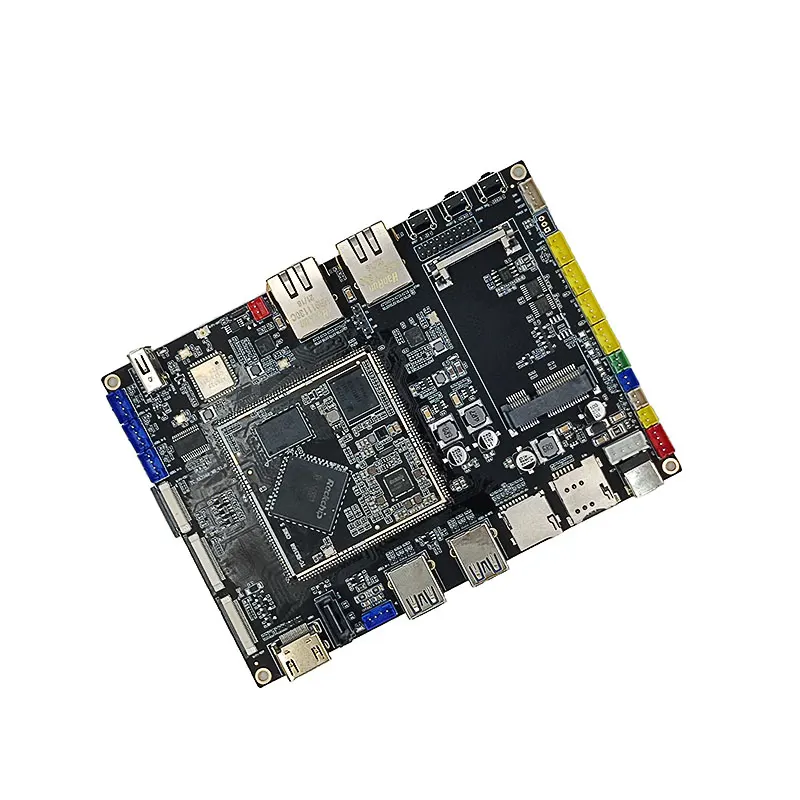

RK3568 Development Board

RK3568, quad-core 64-bit Cortex-A55-processoren, med 22nm litografiproces, har en frekvens på op til 2.0GHz, der leverer effektiv og stabil ydeevne til databehandling af backend-udstyr. Der er en række forskellige opbevaringsmuligheder, som giver kunderne mulighed for hurtigt at implementere forskning og produktion af produkter. Den understøtter op til 8GB RAM, med op til 32Bit bredde og frekvens op til 1600MHz. Det understøtter all-data-link ECC, hvilket gør data sikrere og mere pålidelige og opfylder kravene til at køre produkter med stor hukommelse. Den er integreret med dual-core GPU, højtydende VPU og højeffektiv NPU. GPU'en understøtter OpenGL ES3.2/2.0/1.1, Vulkan1.1. VPU'en kan opnå 4K 60fps H.265/H.264/VP9 videoafkodning og 1080P 100fps H.265/H.264 videokodning. NPU'en understøtter et-klik-skift af almindelige rammer som Caffe/TensorFlow.

Send forespørgsel Download PDF

Thinkcore TC-RK3568 Stamp Hole Development Board Specifikation

Ophavsretserklæring

Ophavsretten til denne vejledning tilhører Shenzhen Thinkcore Technology Co., Ltd., og alle rettigheder er forbeholdt. Virksomheder eller enkeltpersoner har ikke tilladelse til at udtrække en del af eller hele denne manual, og overtrædere vil blive retsforfulgt i henhold til loven.

Opmærksomhed:

Manualerne til udviklingsplatformen ved salg vil blive opdateret fra tid til anden, download venligst den seneste manual fra hjemmesiden www.think-core.com eller kontakt vores virksomheds salgsrepræsentant, der vil ikke være yderligere varsel.

Release Note

|

Version |

Dato |

Forfatter |

Beskrivelse |

|

Rev.01 |

2022-08-04 |

|

Revision |

Kapitel 1. TC-RK3568 Stamp Hole Development Board Introduktion

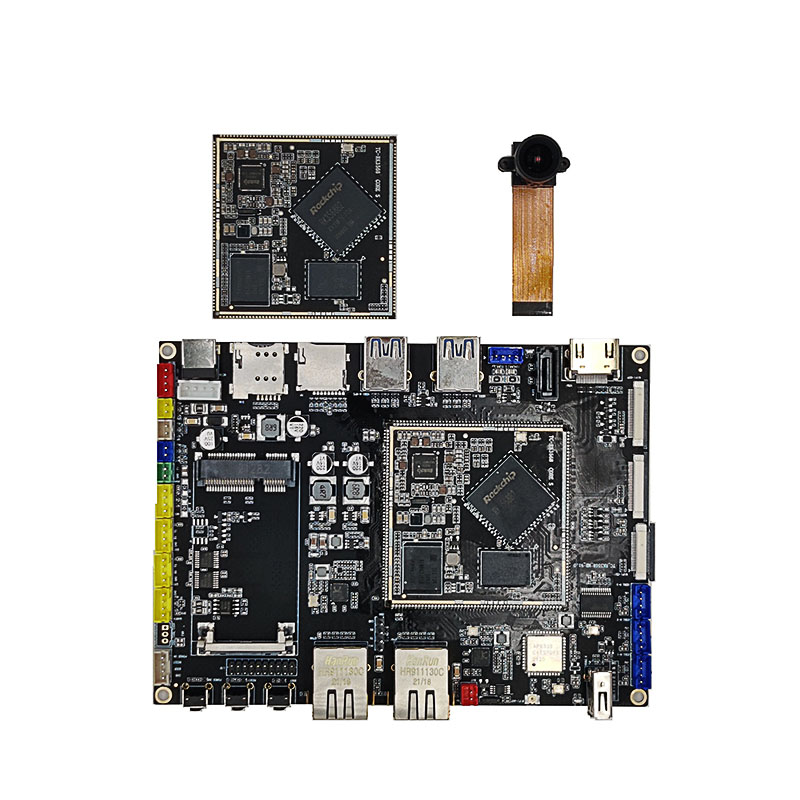

TC-RK3568 Stamp Hole Development Board Brief

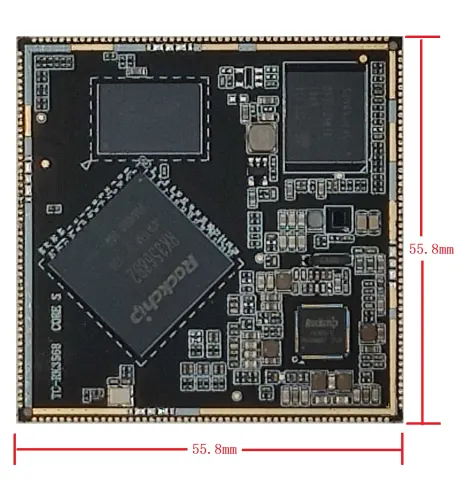

TC-RK3568 Stamp Hole Development Board inkluderer TC-RK3568 Stamp Hole SOM og bærebarord.

TC-RK3568 Stamp Hole-system på modulet er udstyret med Rockchip 64-bit processor RK3568, som er konfigureret med dual-core GPU og højtydende NPU.

RK3568, quad-core 64-bit Cortex-A55-processoren, med 22nm litografiproces, har en frekvens på op til 2.0GHz, der leverer effektiv og stabil ydeevne til databehandling af backend-udstyr. Der er en række forskellige opbevaringsmuligheder, som giver kunderne mulighed for hurtigt at implementere forskning og produktion af produkter. Den understøtter op til 8GB RAM, med op til 32Bit bredde og frekvens op til 1600MHz. Det understøtter all-data-link ECC, hvilket gør data sikrere og mere pålidelige og opfylder kravene til at køre produkter med stor hukommelse. Den er integreret med dual-core GPU, højtydende VPU og højeffektiv NPU. GPU'en understøtter OpenGL ES3.2/2.0/1.1, Vulkan1.1. VPU'en kan opnå 4K 60fps H.265/H.264/VP9 videoafkodning og 1080P 100fps H.265/H.264 videokodning. NPU'en understøtter et-klik-skift af almindelige rammer som Caffe/TensorFlow.

Med MIPI-CSI x2, MIPI-DSI x2, HDMI2.0, EDP-videogrænseflader kan den understøtte op til tre skærmudgange med forskellig skærm. Den indbyggede 8M ISP understøtter dobbeltkameraer og HDR. Video input interface kan tilsluttes et eksternt kamera eller flere kameraer. Den er udstyret med dobbelte adaptive RJ45 Gigabit Ethernet-porte, hvorigennem interne og eksterne netværksdata kan tilgås og transmitteres, hvilket forbedrer netværkstransmissionseffektiviteten og opfylder behovene for produkter med flere netværksporte såsom NVR og industriel gateway.

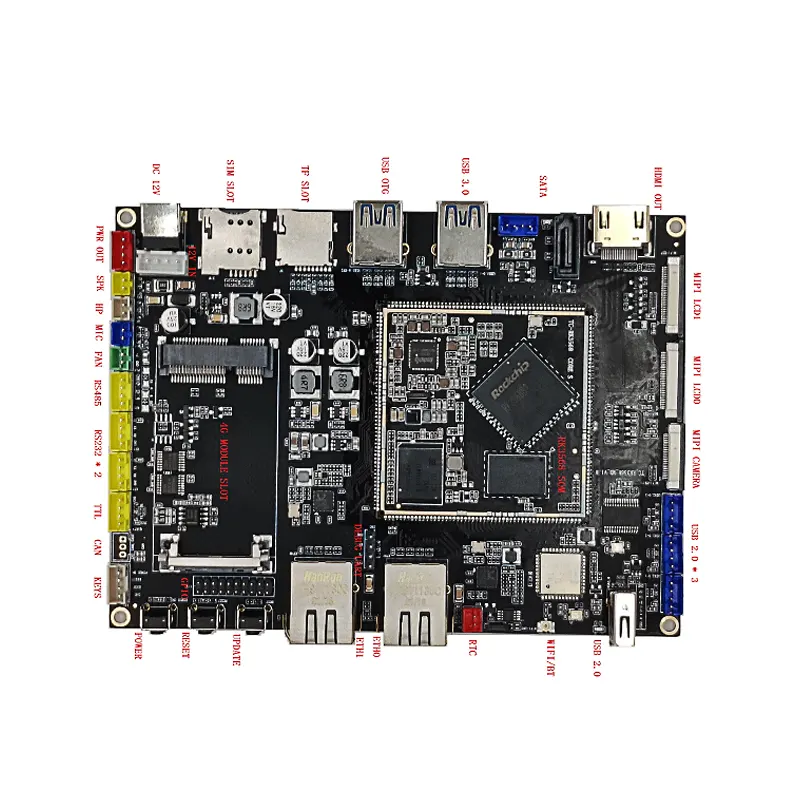

Bærekortet indeholder mange grænseflader, såsom 4G LTE-port, USB3.0, USB2.0, PCIE, dual Ethernet, WIFI, Bluetooth, Audio input og output, HDMI out, MIPI DSI display, eDP display, LVDS display, MIPI CSI kamera, TF Card slot, RS485, RS232, TTL, CAN, Power out, SATA osv.

Android 11, Ubuntu 18.04 OS, Debian OS og Linux Buildroot understøttes. Den stabile og pålidelige drift giver et sikkert og stabilt systemmiljø til produktforskning og produktion.

Et komplet SDK, udviklingsdokumenter, eksempler, teknologidokumenter, tutorials og andre ressourcer er tilvejebragt, så brugerne kan foretage en yderligere tilpasning.

TC-RK3568 Stamp Hole Development Board Funktioner:

Størrelse: 150mm x 110mm.

Rich grænseflader, kan bruges direkte i forskellige intelligente produkter for at lette færdiggørelsen af produkter.

Android 11.0, Ubuntu 18.04 OS, Debian OS og Linux Buildroot understøttes.

Ansøgning

Dette board kan bruges i vid udstrækning i smarte NVR'er, cloud-terminaler, IoT-gateways, industriel kontrol, edge computing, ansigtsgenkendelsesporte, NAS'er, køretøjscenterkonsoller osv.

Karakteristisk parameter

|

specifikationer |

|

|

CPU |

RockChip RK3568, Quad-core 64-bit Cortex-A55, 22nm litografiproces, frekvens op til 2,0GHz |

|

GPU |

ARM G52 2EE Understøtter OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 Indlejret højtydende 2D-accelerationshardware |

|

NPU |

0.8Tops@INT8, integreret højtydende AI-accelerator RKNN NPU Understøtter et-klik skift af Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet |

|

VPU |

Understøtter 4K 60fps H.265/H.264/VP9 videoafkodning Understøtter 1080P 100fps H.265/H.264 videokodning Understøtter 8M ISP, understøtter HDR |

|

vædder |

2GB/4GB/8GB |

|

Opbevaring |

8GB/16GB/32GB/64GB/128GB eMMC Understøtter SATA 3.0 x 1 (Udvid med 2.5â SSD/HDD) Understøtter TF-Card Slot x1 (Udvid med TF-kort) |

|

System OS |

Android11/Linux Buildroot/Ubuntu/Debian |

|

Hardwarefunktioner |

|

|

Skærm |

1 * HDMI2.0, understøtter 4K@60fps output 1 * MIPI DSI, understøtter 1920*1080@60fps output 1 * LVDS, understøtter 1920*1080@60fps output 1 * eDP1.3, understøtter 2560x1600@60fps output |

|

Ethernet |

Understøtter to Gigabit Ethernet-porte (1000 Mbps) |

|

trådløst internet |

Mini PCIe til tilslutning af 4G LTE Understøtter WiFi 6 (802.11 AX) Understøtter BT5.0 |

|

PCIE3.0 |

Understøtter PCE3.0 interface |

|

Lyd |

1 * HDMI lydudgang 1 * Højttalerudgang 1 * Høretelefonudgang 1 * Mikrofon indbygget lydindgang |

|

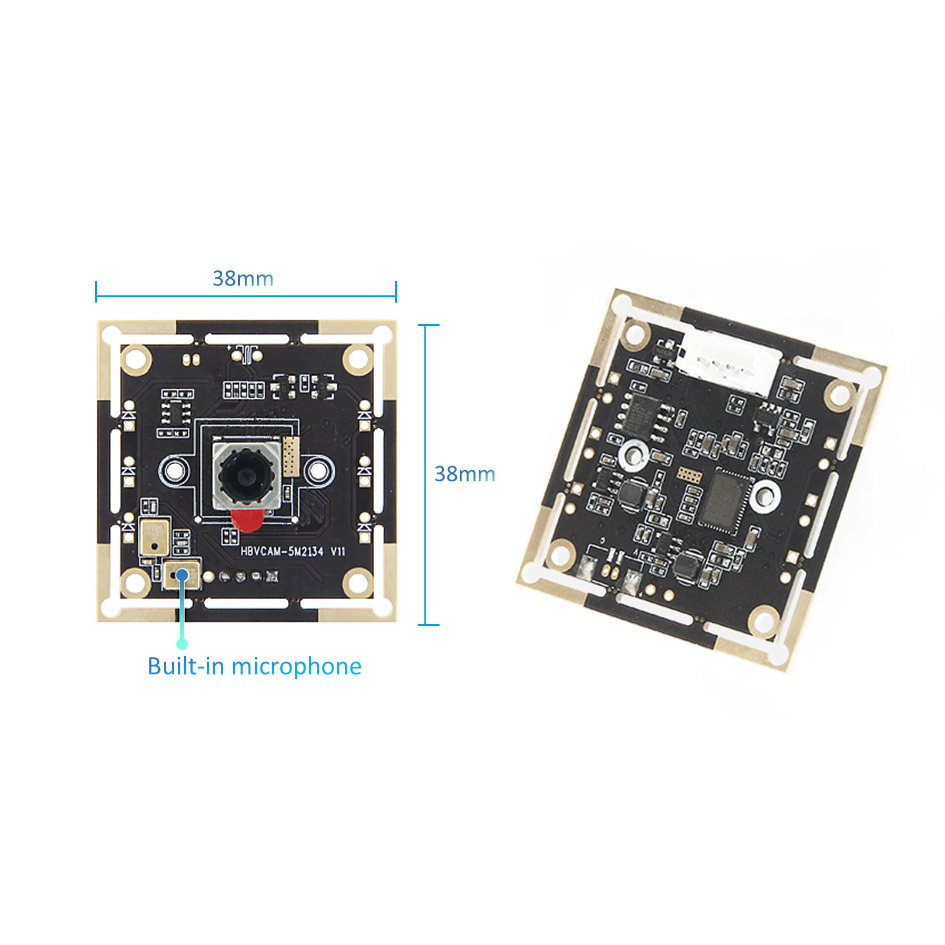

Kamera |

Understøtter 1-kanals MIPI-CSI kamera interface Understøtter HDR, billedet forbliver klart under modlys eller stærke lysforhold

|

|

USB |

1 * USB3.0 Host, 4* USB 2.0 Host, 1 * USB3.0 OTG |

|

SATA |

1 * SATA, 6,0 Gb/s |

|

Seriel |

1 * TTL, 2 * RS232, 1 * RS485 |

|

KAN |

Understøtter CAN2.0B, Understøtter 1 Mbps, 8 Mbps |

|

TF kort |

1 * TF-kortplads |

|

Andre |

GPIO og ADC |

|

Størrelse |

150mm*110mm |

|

|

|

|

Indgangsspænding |

12V/3A |

|

Stuetemperatur

|

-30~80â |

|

Driftstemperatur |

-20~60â |

|

Opbevaring Fugtighed |

10%~80% |

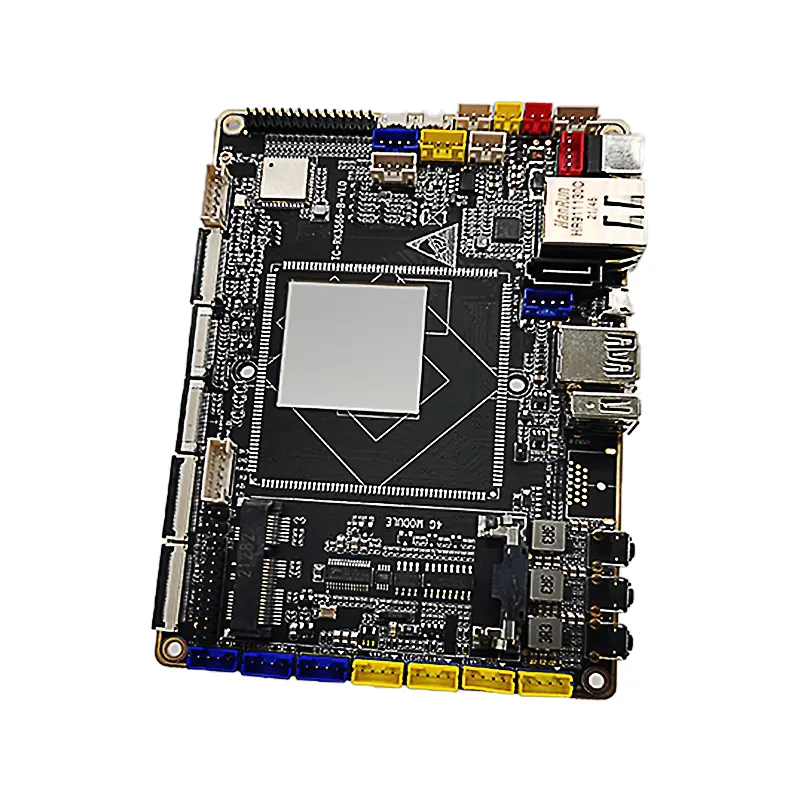

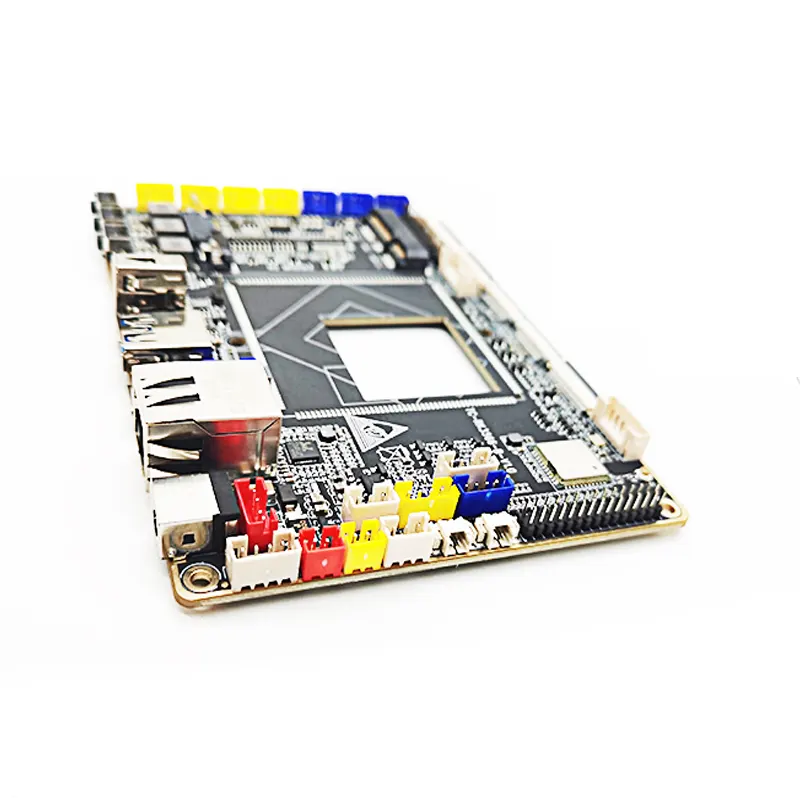

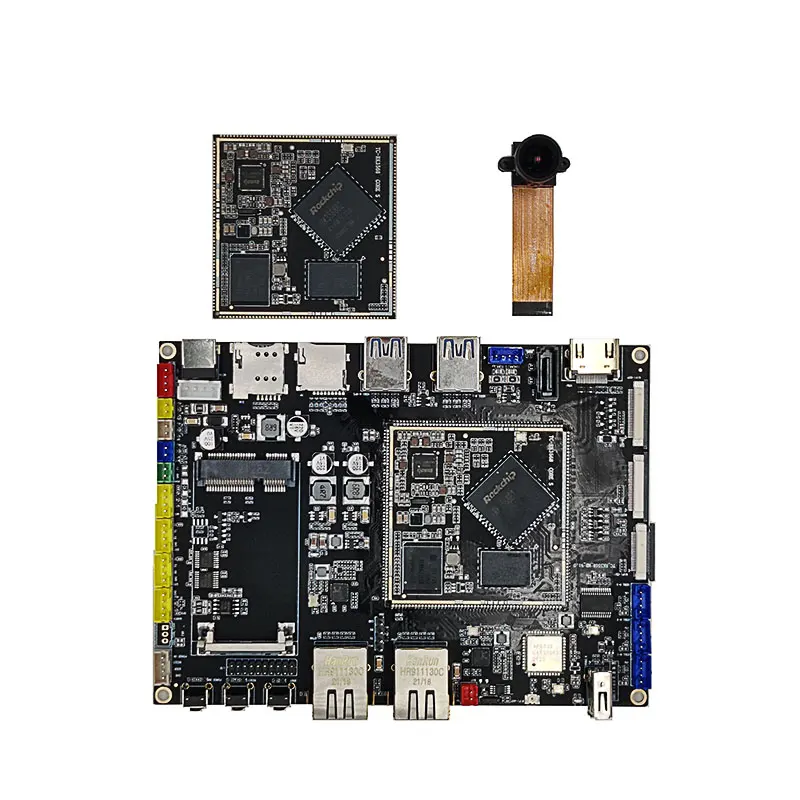

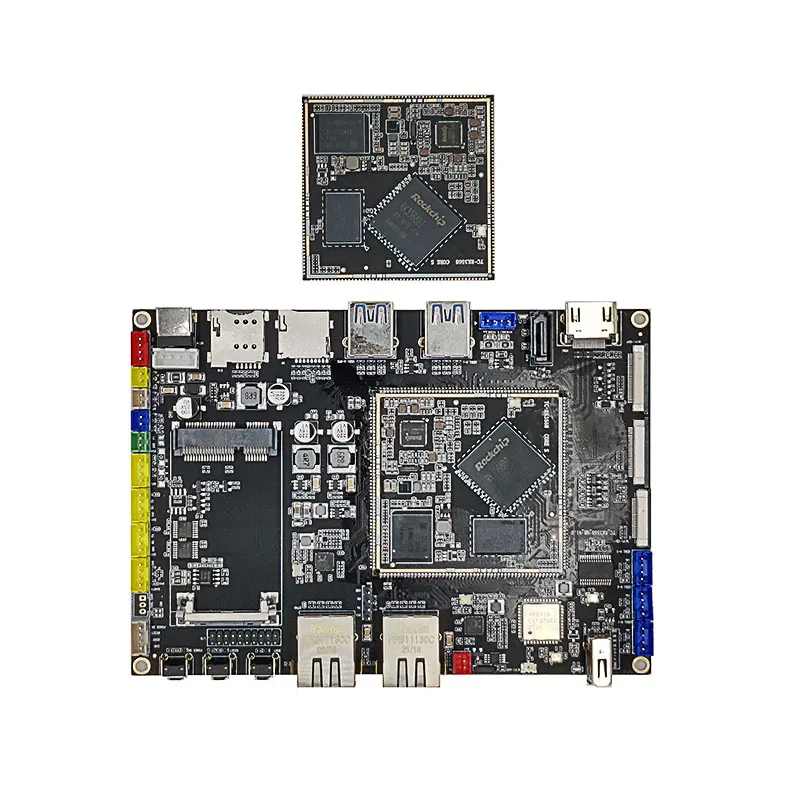

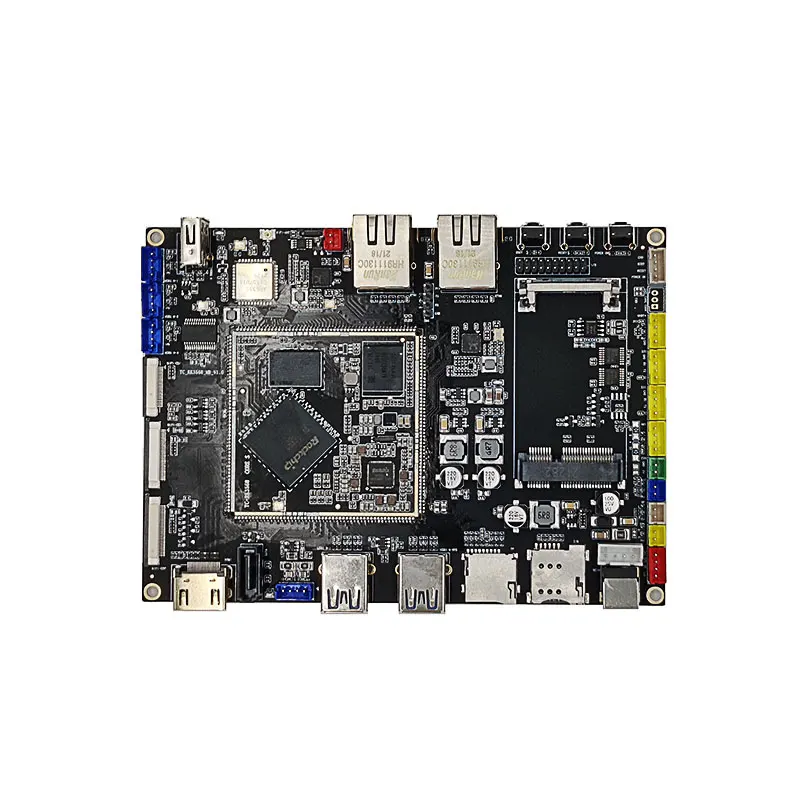

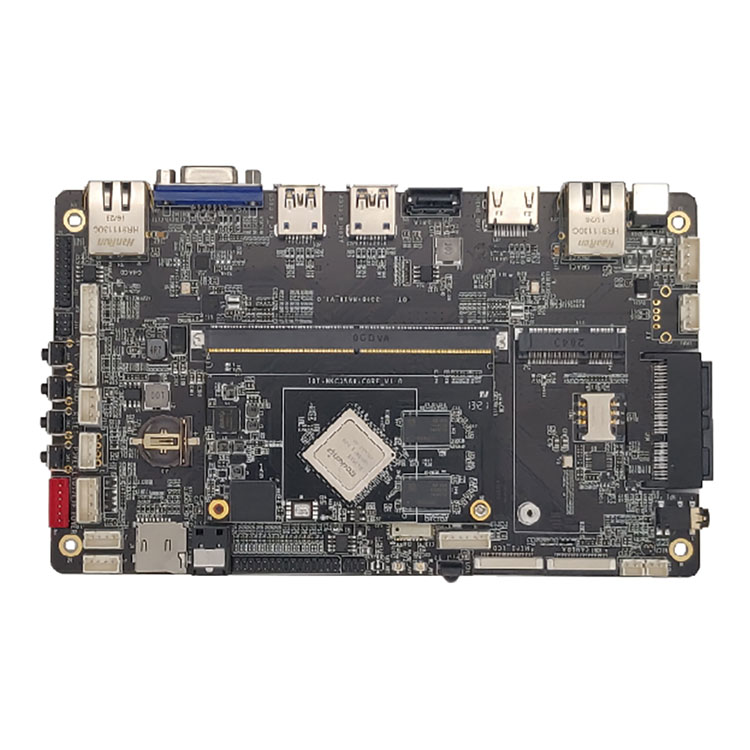

SOM Udseende

SOM foran

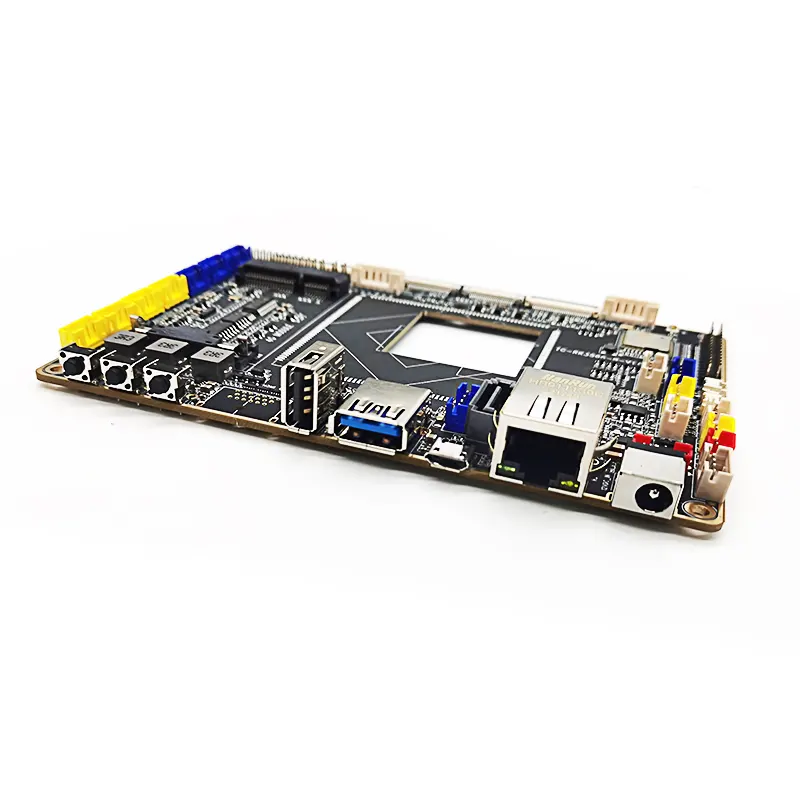

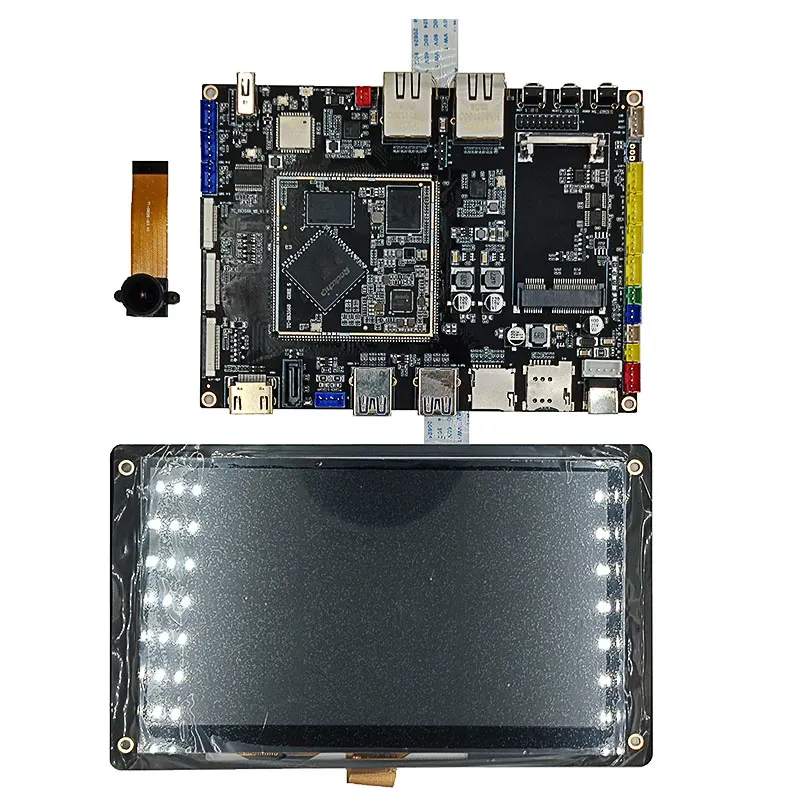

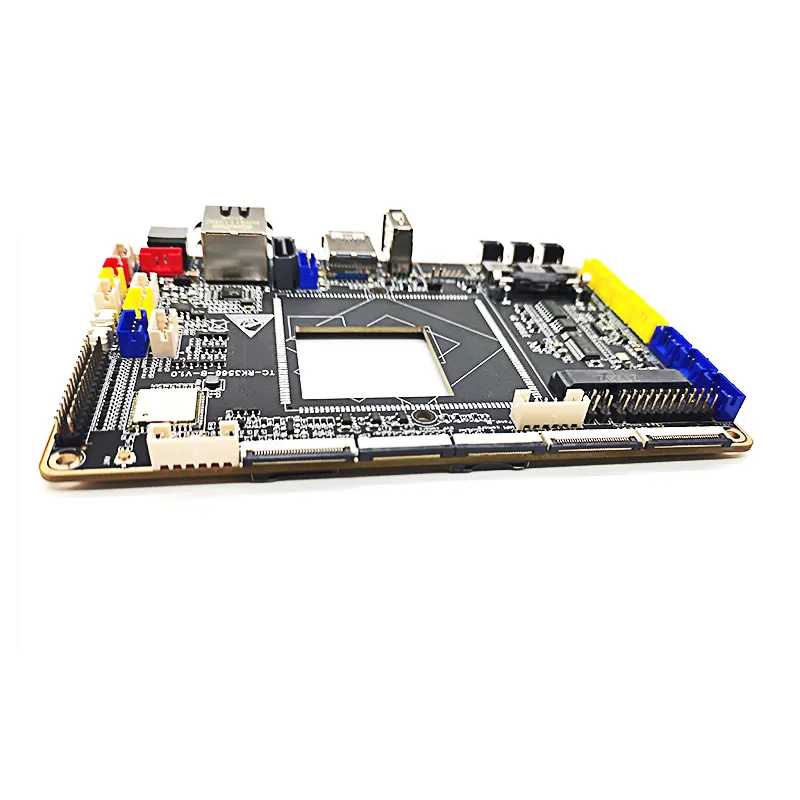

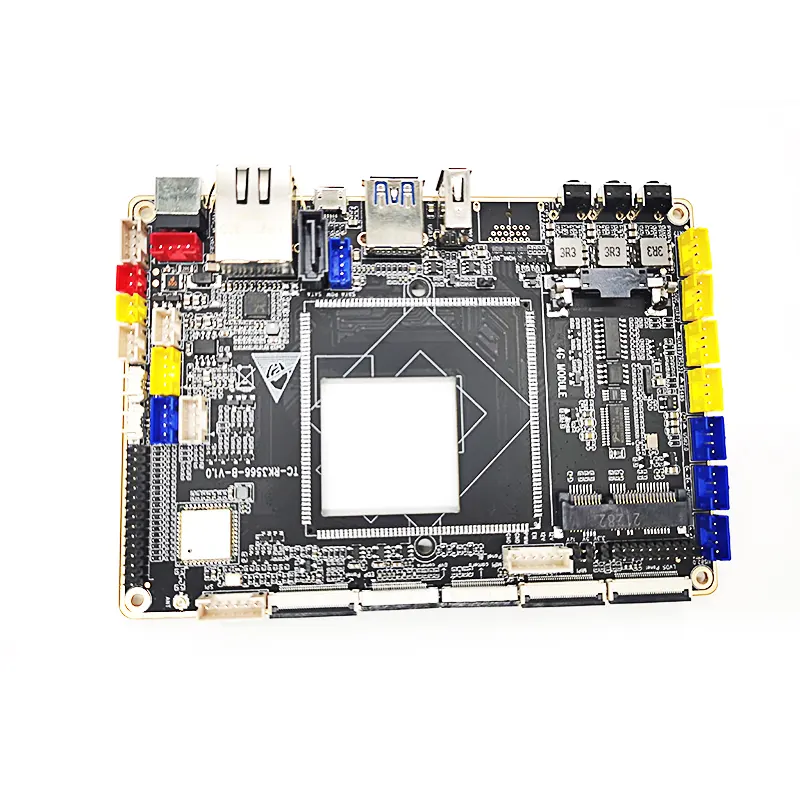

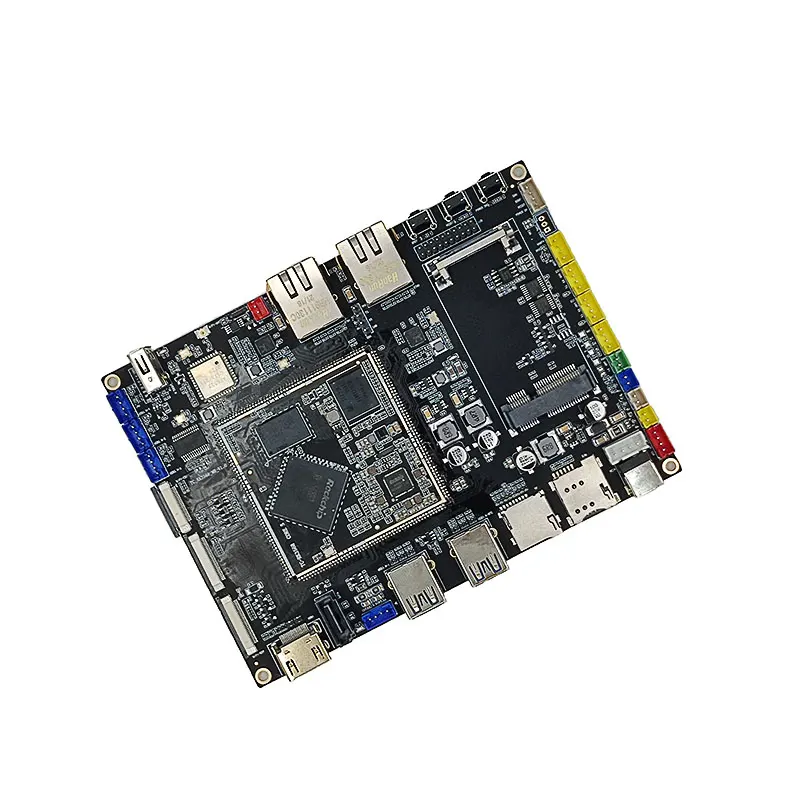

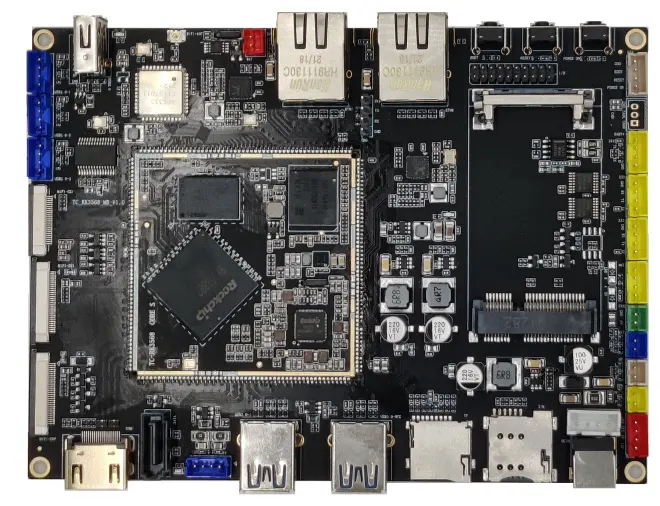

Udviklingsnævnets udseende

Kapitel 2. SOM PIN-definition

SOM PIN-definition

|

PIN |

Definition af kernepladestift |

Standard funktion |

Standard funktionsbeskrivelse |

IO Power |

Pad type IO træk |

|

1 |

VCC3V3_SYS |

3,3V system strømforsyning |

Indgangsspænding 3,3V |

|

- |

|

2 |

VCC3V3_SYS |

3,3V system strømforsyning |

Indgangsspænding 3,3V |

|

- |

|

3 |

GND |

GND |

GND |

|

- |

|

4 |

GND |

GND |

GND |

|

- |

|

5 |

SDMMC0_DET_L |

SDMMC0_DET/SATA_CP_DET/PCIE30X1_CLKREQn_M0/GPIO0_A4_u |

SDMMC0 detekterer input |

3,3V |

I/O OP |

|

6 |

SDMMC0_D3 |

SDMMC0_D3/ARMJTAG_TMS/UART5_RTSn_M0/GPIO2_A0_u |

SDMMC0 dataport |

3,3V |

I/O OP

|

|

7 |

SDMMC0_D2 |

SDMMC0_D2/ARMJTAG_TCK/UART5_CTSn_M0/GPIO1_D7_u |

SDMMC0 dataport |

3,3V |

I/O OP

|

|

8 |

SDMMC0_D1 |

SDMMC0_D1/UART2_RX_M1/UART6_RX_M1/PWM9_M1/GPIO1_D6_u |

SDMMC0 dataport |

3,3V |

I/O OP

|

|

9 |

SDMMC0_D0 |

SDMMC0_D0/UART2_TX_M1/UART6_TX_M1/PWM8_M1/GPIO1_D5_u |

SDMMC0 dataport |

3,3V |

I/O OP

|

|

10 |

SDMMC0_CMD |

SDMMC0_CMD/PWM10_M1/UART5_RX_M0/CAN0_TX_M1/GPIO2_A1_u |

SDMMC0 kommando output |

3,3V |

I/O OP

|

|

11 |

SDMMC0_CLK |

SDMMC0_CLK/TEST_CLKOUT/UART5_TX_M0/CAN0_RX_M1/GPIO2_A2_d |

SDMMC0 urudgang

|

3,3V |

I/O NED |

|

12 |

NULSTIL |

NPOR_U |

Nulstil signalregistrering |

3,3V |

- |

|

13 |

RK809_PWRON |

Tænd |

Tænd signalindgang, ekstern forbindelse tænd/sluk-tast, aktiv lav |

|

- |

|

14 |

GENOPRETNING |

SARADC_VIN0 |

AD-tastaturinput |

1,8V |

- |

|

15 |

EXT_DA |

EXT_DA |

Aktiver PMIC Power |

|

- |

|

16 |

HPR_OUT |

HPR_OUT |

Hovedtelefoner lige ud |

3,3V |

- |

|

17 |

HPL_OUT |

HPL_OUT |

Hovedtelefoner udeladt |

3,3V |

- |

|

18 |

SPKP_OUT |

SPKP_OUT |

Tale ud |

5V/0,6W |

- |

|

19 |

SPKN_OUT |

SPKN_OUT |

Tale ud- |

5V/0,6W |

- |

|

20 |

MIC1_INN |

MIC1_INN/MIC_R |

MIC1_INN |

3,3V |

- |

|

21 |

MIC1_INP |

MIC1_INP/MIC_L |

MIC1_INP |

3,3V |

- |

|

22 |

HP_DET_L_GPIO3_C2 |

LCDC_VSYNC/VOP_BT1120_D14/SPI1_MISO_M1/UART5_TX_M1/I2S1_SDO3_M2/GPIO3_C2_d |

Hovedtelefonregistrering |

3,3V |

I/O NED |

|

23 |

SPK_CTL_H_GPIO3_C3 |

LCDC_DEN/VOP_BT1120_D15/SPI1_CLK_M1/UART5_RX_M1/I2S1_SCLK_RX_M2/GPIO3_C3_d |

|

3,3V |

I/O NED |

|

24 |

VCC3V3_SD |

3,3V strømforsyning |

Udgangsspænding 3,3V til SD-kort, nominel udgangsstrøm 2A |

|

- |

|

25 |

VCC_3V3 |

3,3V strømforsyning |

Udgangsspænding 3,3V, nominel udgangsstrøm 2A |

|

- |

|

26 |

VCC_1V8 |

1,8V strømforsyning |

Udgangsspænding 1,8V, nominel udgangsstrøm 2,5A |

|

- |

|

27 |

PDM_SDI1_M0_ADC |

I2S1_SDO3_M0/I2S1_SDI1_M0/PDM_SDI1_M0/PCIE20_PERSTn_M2/GPIO1_B2_d |

PDM_SDI1_M0_ADC |

3,3V |

IO NED |

|

28 |

PDM_SDI2_M0_ADC |

I2S1_SDO2_M0/I2S1_SDI2_M0/PDM_SDI2_M0/PCIE20_WAKEn_M2/ACODEC_ADC_SYNC/GPIO1_B1_d |

PDM_SDI2_M0_ADC |

3,3V |

IO NED |

|

29 |

PDM_SDI3_M0_ADC |

I2S1_SDO1_M0/I2S1_SDI3_M0/PDM_SDI3_M0/PCIE20_CLKREQn_M2/ACODEC_DAC_DATAR/GPIO1_B0_d |

PDM_SDI3_M0_ADC |

3,3V |

IO NED |

|

30 |

PDM_CLK1_M0_ADC |

I2S1_SCLK_RX_M0/UART4_RX_M0/PDM_CLK1_M0/SPDIF_TX_M0/GPIO1_A4_d |

PDM_CLK1_M0_ADC |

3,3V |

IO NED |

|

31 |

GMAC0_TXD0 |

GMAC0_TXD0/UART1_RX_M0/GPIO2_B3_u |

GMAC0 overfører data |

1,8V |

I/O OP |

|

32 |

GMAC0_TXD1 |

GMAC0_TXD1/UART1_TX_M0/GPIO2_B4_u |

GMAC0 overfører data |

1,8V |

I/O OP |

|

33 |

GMAC0_TXD2 |

SDMMC1_D3/GMAC0_TXD2/UART7_TX_M0/GPIO2_A6_u |

GMAC0 overfører data |

1,8V |

I/O OP |

|

34 |

GMAC0_TXD3 |

SDMMC1_CMD/GMAC0_TXD3/UART9_RX_M0/GPIO2_A7_u |

GMAC0 overfører data |

1,8V |

I/O OP |

|

35 |

GMAC0_TXEN |

GMAC0_TXEN/UART1_RTSn_M0/SPI1_CLK_M0/GPIO2_B5_u |

GMAC0 sende aktiveret |

1,8V |

I/O OP |

|

36 |

GMAC0_TXCLK |

SDMMC1_CLK/GMAC0_TXCLK/UART9_TX_M0/GPIO2_B0_d |

GMAC0 sender ur |

1,8V |

I/O NED |

|

37 |

GMAC0_RXD0 |

GMAC0_RXD0/UART1_CTSn_M0/SPI1_MISO_M0/GPIO2_B6_u |

GMAC0 modtager data |

1,8v |

I/O OP |

|

38 |

GMAC0_RXD1 |

I2S2_SCLK_RX_M0/GMAC0_RXD1/UART6_RTSn_M0/SPI1_MOSI_M0/GPIO2_B7_d |

GMAC0 modtager data |

1,8V |

I/O NED |

|

39 |

GMAC0_RXD2 |

SDMMC1_D0/GMAC0_RXD2/UART6_RX_M0/GPIO2_A3_u |

GMAC0 modtager data |

1,8v |

I/O OP |

|

40 |

GMAC0_RXD3 |

SDMMC1_D1/GMAC0_RXD3/UART6_TX_M0/GPIO2_A4_u |

GMAC0 modtager data |

1,8V |

I/O OP |

|

41 |

GMAC0_RXDV_CRS |

I2S2_LRCK_RX_M0/GMAC0_RXDV_CRS/UART6_CTSn_M0/SPI1_CS0_M0/GPIO2_C0_d |

GMAC0 RX data gyldigt signal |

1,8V |

I/O NED |

|

42 |

GMAC0_RXCLK |

SDMMC1_D2/GMAC0_RXCLK/UART7_RX_M0/GPIO2_A5_u |

GMAC0 modtager ur |

1,8V |

I/O OP |

|

43 |

ETH0_REFCLKO_25M |

I2S2_MCLK_M0/ETH0_REFCLKO_25M/UART7_RTSn_M0/SPI2_CLK_M0/GPIO2_C1_d |

ETH0_REF CLOCK OUTPUT_25MHz CPU til PHY, standard NC |

1,8V |

I/O NED |

|

44 |

GMAC0_MCLKINOUT |

I2S2_SCLK_TX_M0/GMAC0_MCLKINOUT/UART7_CTSn_M0/SPI2_MISO_M0/GPIO2_C2_d |

GMAC0 eksternt ur |

1,8V |

I/O NED |

|

45 |

GMAC0_MDC |

I2S2_LRCK_TX_M0/GMAC0_MDC/UART9_RTSn_M0/SPI2_MOSI_M0/GPIO2_C3_d |

MAC0 management ur |

1,8V |

I/O NED |

|

46 |

GMAC0_MDIO |

I2S2_SDO_M0/GMAC0_MDIO/UART9_CTSn_M0/SPI2_CS0_M0/GPIO2_C4_d |

MAC0 management kommando og data |

1,8V |

I/O NED |

|

47 |

GMAC0_RSTN_GPIO3_B7 |

LCDC_D21/VOP_BT1120_D12/GMAC1_TXD1_M0/I2C3_SDA_M1/PWM11_IR_M0/GPIO3_B6_d |

|

3,3V |

IO NED |

|

48 |

GMAC0_INT_PMEB_GPIO3_C0 |

LCDC_HSYNC/VOP_BT1120_D13/SPI1_MOSI_M1/PCIE20_PERSTn_M1/I2S1_SDO2_M2/GPIO3_C1_d |

|

3,3V |

I/O NED |

|

49 |

RTCTC_INT_L_GPIO0_D3 |

GPIO0_D3_d |

RTC_IC_INT, aktiv lav |

1,8V |

I/O NED |

|

50 |

I2C5_SDA_M0 |

LCDC_D19/VOP_BT1120_D10/GMAC1_RXER_M0/I2C5_SDA_M0/PDM_SDI1_M2/GPIO3_B4_d |

I2C seriel port 5 |

3,3V |

I/O NED |

|

51 |

I2C5_SCL_M0 |

LCDC_D18/VOP_BT1120_D9/GMAC1_RXDV_CRS_M0/I2C5_SCL_M0/PDM_SDI0_M2/GPIO3_B3_d |

I2C seriel port 5 |

3,3V |

I/O NED |

|

52 |

PWM3_IR |

PWM3_IR/EDP_HPDIN_M1/PCIE30X1_WAKEn_M0/MCU_JTAG_TMS/GPIO0_C2_d |

|

3,3V |

I/O NED |

|

53 |

CAN1_TX_M1 |

PWM15_IR_M1/SPI3_MOSI_M1/CAN1_TX_M1/PCIE30X2_WAKEn_M2/I2S3_SCLK_M1/GPIO4_C3_d |

KAN data overføre |

3,3V |

I/O NED |

|

54 |

CAN1_RX_M1 |

PWM14_M1/SPI3_CLK_M1/CAN1_RX_M1/PCIE30X2_CLKREQn_M2/I2S3_MCLK_M1/GPIO4_C2_d |

KAN modtage data |

3,3V |

I/O NED |

|

55 |

UART2_RX_M0_DEBUG |

UART2_RX_M0/GPIO0_D0_u |

UART seriel port |

3,3V |

I/O OP |

|

56 |

UART2_TX_M0_DEBUG |

UART2_TX_M0/GPIO0_D1_u |

UART seriel port datatransmission til debug |

3,3V |

I/O OP |

|

57 |

UART3_RX_M1 |

LCDC_D23/PWM13_M0/GMAC1_MCLKINOUT_M0/UART3_RX_M1/PDM_SDI3_M2/GPIO3_C0_d |

UART serial port data modtagelse |

3,3V |

I/O NED |

|

58 |

UART3_TX_M1 |

LCDC_D22/PWM12_M0/GMAC1_TXEN_M0/UART3_TX_M1/PDM_SDI2_M2/GPIO3_B7_d |

UART serial port datatransmission |

3,3V |

I/O NED |

|

59 |

UART4_TX_M1 |

LCDC_D17/VOP_BT1120_D8/GMAC1_RXD1_M0/UART4_TX_M1/PWM9_M0/GPIO3_B2_d |

UART serial port datatransmission |

3,3V |

I/O NED |

|

60 |

UART4_RX_M1 |

LCDC_D16/VOP_BT1120_D7/GMAC1_RXD0_M0/UART4_RX_M1/PWM8_M0/GPIO3_B1_d |

UART serial port data modtagelse |

3,3V |

I/O NED |

|

61 |

UART9_RX_M1 |

PWM13_M1/SPI3_CS0_M1/SATA0_ACT_LED/UART9_RX_M1/I2S3_SDI_M1/GPIO4_C6_d |

UART serial port data modtagelse |

3,3V |

I/O NED |

|

62 |

UART9_TX_M1 |

PWM12_M1/SPI3_MISO_M1/SATA1_ACT_LED/UART9_TX_M1/I2S3_SDO_M1/GPIO4_C5_d |

UART serial port datatransmission |

3,3V |

I/O NED |

|

63 |

UART7_RX_M1 |

PWM15_IR_M0/SPDIF_TX_M1/GMAC1_MDIO_M0/UART7_RX_M1/I2S1_LRCK_RX_M2/GPIO3_C5_d |

UART serial port data modtagelse |

3,3V |

I/O NED |

|

64 |

UART7_TX_M1 |

PWM14_M0/VOP_PWM_M1/GMAC1_MDC_M0/UART7_TX_M1/PDM_CLK1_M2/GPIO3_C4_d |

UART serial port datatransmission |

3,3V |

I/O NED |

|

65 |

RS485_DIR_GPIO3_B5 |

LCDC_D20/VOP_BT1120_D11/GMAC1_TXD0_M0/I2C3_SCL_M1/PWM10_M0/GPIO3_B5_d |

RS485 data retning |

3,3V |

I/O NED |

|

66 |

DVP_PWREN0_H_GPIO0_B0 |

CLK32K_IN/CLK32K_OUT0/PCIE30X2_BUTTONRSTn/GPIO0_B0_u |

|

3,3V |

I/O OP |

|

67 |

WIFI_PWREN_L_GPIO0_C1 |

PWM2_M0/NPUAVS/UART0_TX/MCU_JTAG_TDI/GPIO0_C1_d |

|

3,3V |

I/O NED |

|

68 |

I2S3_SDI_M0 |

LCDC_D13/VOP_BT1120_CLK/GMAC1_TXCLK_M0/I2S3_SDI_M0/SDMMC2_CLK_M1/GPIO3_A6_d |

I2S3_SDI |

3,3V |

I/O NED |

|

69 |

I2S3_SDO_M0 |

LCDC_D12/VOP_BT1120_D4/GMAC1_RXD3_M0/I2S3_SDO_M0/SDMMC2_CMD_M1/GPIO3_A5_d |

I2S3_SDO |

3,3V |

I/O NED |

|

70 |

I2S3_LRCK_M0 |

LCDC_D11/VOP_BT1120_D3/GMAC1_RXD2_M0/I2S3_LRCK_M0/SDMMC2_D3_M1/GPIO3_A4_d |

I2S3_LRCK |

3,3V |

I/O NED |

|

71 |

I2S3_SCLK_M0 |

LCDC_D10/VOP_BT1120_D2/GMAC1_TXD3_M0/I2S3_SCLK_M0/SDMMC2_D2_M1/GPIO3_A3_d |

I2S3_SCLK |

3,3V |

I/O NED |

|

72 |

HOST_WAKE_BT_H_GPIO3_A2 |

LCDC_D9/VOP_BT1120_D1/GMAC1_TXD2_M0/I2S3_MCLK_M0/SDMMC2_D1_M1/GPIO3_A2_d |

HOST_WAKE_BT |

3,3V |

I/O NED |

|

73 |

BT_WAKE_HOST_H_GPIO3_A1 |

LCDC_D8/VOP_BT1120_D0/SPI1_CS0_M1/PCIE30X1_PERSTn_M1/SDMMC2_D0_M1/GPIO3_A1_d |

BT_WAKE_HOST |

3,3V |

I/O NED |

|

74 |

BT_REG_ON_H_GPIO3_A0 |

LCDC_CLK/VOP_BT656_CLK_M0/SPI2_CLK_M1/UART8_RX_M1/I2S1_SDO1_M2/GPIO3_A0_d |

Bluetooth-modul strømaktiveret |

3,3V |

I/O NED |

|

75 |

UART8_RX_M0 |

CLK32K_OUT1/UART8_RX_M0/SPI1_CS1_M0/GPIO2_C6_d |

UART serial port data modtagelse |

1,8V |

I/O NED |

|

76 |

UART8_TX_M0 |

I2S2_SDI_M0/GMAC0_RXER/UART8_TX_M0/SPI2_CS1_M0/GPIO2_C5_d |

UART serial port datatransmission |

1,8V |

I/O NED |

|

77 |

UART8_CTSN_M0 |

SDMMC1_DET/I2C4_SCL_M1/UART8_CTSn_M0/CAN2_TX_M1/GPIO2_B2_u |

UART8_CTSn_M0 |

1,8V |

I/O NED |

|

78 |

UART8_RTSN_M0 |

SDMMC1_PWREN/I2C4_SDA_M1/UART8_RTSn_M0/CAN2_RX_M1/GPIO2_B1_d |

UART8_RTSn_M0 |

1,8V |

I/O NED |

|

79 |

WIFI_REG_ON_H_GPIO3_D5 |

CIF_D7/EBC_SDDO7/SDMMC2_PWREN_M0/I2S1_SDI3_M1/VOP_BT656_D7_M1/GPIO3_D5_d |

WIFI_REG aktivere |

1,8V |

I/O NED |

|

80 |

WIFI_WAKE_HOST_H_GPIO3_D4 |

CIF_D6/EBC_SDDO6/SDMMC2_DET_M0/I2S1_SDI2_M1/VOP_BT656_D6_M1/GPIO3_D4_d |

WIFI wake up vært |

1,8V |

I/O NED |

|

81 |

SDMMC2_CLK_M0 |

CIF_D5/EBC_SDDO5/SDMMC2_CLK_M0/I2S1_SDI1_M1/VOP_BT656_D5_M1/GPIO3_D3_d |

SDMMC2 ur |

1,8V |

I/O NED |

|

82 |

SDMMC2_CMD_M0 |

CIF_D4/EBC_SDDO4/SDMMC2_CMD_M0/I2S1_SDI0_M1/VOP_BT656_D4_M1/GPIO3_D2_d |

SDMMC2 kommando |

1,8V |

I/O NED |

|

83 |

SDMMC2_D3_M0 |

CIF_D3/EBC_SDDO3/SDMMC2_D3_M0/I2S1_SDO0_M1/VOP_BT656_D3_M1/GPIO3_D1_d |

SDMMC2 data |

1,8V |

I/O NED |

|

84 |

SDMMC2_D2_M0 |

CIF_D2/EBC_SDDO2/SDMMC2_D2_M0/I2S1_LRCK_TX_M1/VOP_BT656_D2_M1/GPIO3_D0_d |

SDMMC2 data |

1,8V |

I/O NED |

|

85 |

SDMMC2_D1_M0 |

CIF_D1/EBC_SDDO1/SDMMC2_D1_M0/I2S1_SCLK_TX_M1/VOP_BT656_D1_M1/GPIO3_C7_d |

SDMMC2 data |

1,8V |

I/O NED |

|

86 |

SDMMC2_D0_M0 |

CIF_D0/EBC_SDDO0/SDMMC2_D0_M0/I2S1_MCLK_M1/VOP_BT656_D0_M1/GPIO3_C6_d |

SDMMC2 data |

1,8V |

I/O NED |

|

87 |

GMAC1_INT/PMEB_GPIO3_A7 |

LCDC_D14/VOP_BT1120_D5/GMAC1_RXCLK_M0/SDMMC2_DET_M1/GPIO3_A7_d |

|

3,3V |

I/O NED |

|

88 |

GMAC1_RSTN_GPIO3_B0 |

LCDC_D15/VOP_BT1120_D6/ETH1_REFCLKO_25M_M0/SDMMC2_PWREN_M1/GPIO3_B0_d |

|

3,3V |

I/O NED |

|

89 |

GMAC1_MDIO_M1 |

IF_VSYNC/EBC_SDOE/GMAC1_MDIO_M1/I2S2_SCLK_TX_M1/GPIO4_B7_d |

GMAC1 management kommando og data |

1,8V |

I/O NED |

|

90 |

GMAC1_MDC_M1 |

CIF_HREF/EBC_SDLE/GMAC1_MDC_M1/UART1_RTSn_M1/I2S2_MCLK_M1/GPIO4_B6_d |

GMAC1 management ur |

1,8V |

I/O NED |

|

91 |

GMAC1_MCLKINOUT_M1 |

CIF_CLKIN/EBC_SDCLK/GMAC1_MCLKINOUT_M1/UART1_CTSn_M1/I2S2_SCLK_RX_M1/GPIO4_C1_d |

GMAC1 eksternt ur |

1,8V |

I/O NED |

|

92 |

ETH1_REFCLKO_25M_M1 |

I2C4_SCL_M0/EBC_GDOE/ETH1_REFCLKO_25M_M1/SPI3_CLK_M0/I2S2_SDO_M1/GPIO4_B3_d |

ETH1 Urudgang |

1,8V |

I/O NED |

|

93 |

GMAC1_RXCLK_M1 |

CIF_D13/EBC_SDDO13/GMAC1_RXCLK_M1/UART7_RX_M2/PDM_SDI3_M1/GPIO4_A3_d |

GMAC1 modtager ur |

1,8V |

I/O NED |

|

94 |

GMAC1_RXDV_CRS_M1 |

ISP_PRELIGHT_TRIG/EBC_SDCE3/GMAC1_RXDV_CRS_M1/I2S1_SDO2_M1/GPIO4_B1_d |

GMAC1 RX data gyldigt signal |

1,8V |

I/O NED |

|

95 |

GMAC1_RXD3_M1 |

CIF_D12/EBC_SDDO12/GMAC1_RXD3_M1/UART7_TX_M2/PDM_SDI2_M1/GPIO4_A2_d |

GMAC1 modtager data |

1,8V |

I/O NED |

|

96 |

GMAC1_RXD2_M1 |

CIF_D11/EBC_SDDO11/GMAC1_RXD2_M1/PDM_SDI1_M1/GPIO4_A1_d |

GMAC1 modtager data |

1,8V |

I/O NED |

|

97 |

GMAC1_RXD1_M1 |

CAM_CLKOUT1/EBC_SDCE2/GMAC1_RXD1_M1/SPI3_MISO_M0/I2S1_SDO1_M1/GPIO4_B0_d |

GMAC1 modtager data |

1,8V |

I/O NED |

|

98 |

GMAC1_RXD0_M1 |

CAM_CLKOUT0/EBC_SDCE1/GMAC1_RXD0_M1/SPI3_CS1_M0/I2S1_LRCK_RX_M1/GPIO4_A7_d |

GMAC1 modtager data |

1,8V |

I/O NED |

|

99 |

GMAC1_TXCLK_M1 |

CIF_D10/EBC_SDDO10/GMAC1_TXCLK_M1/PDM_CLK1_M1/GPIO4_A0_d |

GMAC1 sender ur |

1,8V |

I/O NED |

|

100 |

GMAC1_TXEN_M1 |

ISP_FLASHTRIGOUT/EBC_SDCE0/GMAC1_TXEN_M1/SPI3_CS0_M0/I2S1_SCLK_RX_M1/GPIO4_A6_d |

GMAC1-transmissionsaktivering |

1,8V |

I/O NED |

|

101 |

GMAC1_TXD3_M1 |

CIF_D9/EBC_SDDO9/GMAC1_TXD3_M1/UART1_RX_M1/PDM_SDI0_M1/GPIO3_D7_d |

GMAC1 overfører data |

1,8V |

I/O NED |

|

102 |

GMAC1_TXD2_M1 |

CIF_D8/EBC_SDDO8/GMAC1_TXD2_M1/UART1_TX_M1/PDM_CLK0_M1/GPIO3_D6_d |

GMAC1 overfører data |

1,8V |

I/O NED |

|

103 |

GMAC1_TXD1_M1 |

CIF_D15/EBC_SDDO15/GMAC1_TXD1_M1/UART9_RX_M2/I2S2_LRCK_RX_M1/GPIO4_A5_d |

GMAC1 overfører data |

1,8V |

I/O NED |

|

104 |

GMAC1_TXD0_M1 |

CIF_D14/EBC_SDDO14/GMAC1_TXD0_M1/UART9_TX_M2/I2S2_LRCK_TX_M1/GPIO4_A4_d |

GMAC1 overfører data |

1,8V |

I/O NED |

|

105 |

TP_RST_L_GPIO0_B6 |

I2C2_SDA_M0/SPI0_MOSI_M0/PCIE20_PERSTn_M0/PWM2_M1/GPIO0_B6_u |

Berøringspanel nulstilles |

3,3V |

I/O OP

|

|

106 |

TP_INT_L_GPIO0_B5 |

I2C2_SCL_M0/SPI0_CLK_M0/PCIE20_WAKEn_M0/PWM1_M1/GPIO0_B5_u |

Touchpanel afbryde datainput |

3,3V |

I/O OP |

|

107 |

I2C1_SDA_TP |

I2C1_SDA/CAN0_RX_M0/PCIE20_BUTTONRSTn/MCU_JTAG_TCK/GPIO0_B4_u |

I2C seriel port 1 |

3,3V |

I/O OP |

|

108 |

I2C1_SCL_TP |

I2C1_SCL/CAN0_TX_M0/PCIE30X1_BUTTONRSTn/MCU_JTAG_TDO/GPIO0_B3_u |

I2C seriel port 1 |

3,3V |

I/O OP |

|

109 |

I2C3_SCL_M0 |

I2C3_SCL_M0/UART3_TX_M0/CAN1_TX_M0/AUDIOPWM_LOUT_N/ACODEC_ADC_CLK/GPIO1_A1_u |

I2C seriel port 3 |

3,3V |

I/O OP |

|

110 |

I2C3_SDA_M0 |

I2C3_SDA_M0/UART3_RX_M0/CAN1_RX_M0/AUDIOPWM_LOUT_P/ACODEC_ADC_DATA/GPIO1_A0_u |

I2C seriel port 3 |

3,3V |

I/O OP |

|

111 |

I2C2_SCL_M1 |

I2C2_SCL_M1/EBC_SDSHR/CAN2_TX_M0/I2S1_SDO3_M1/GPIO4_B5_d |

I2C seriel port 2 |

1,8V |

I/O NED |

|

112 |

I2C2_SDA_M1 |

I2C2_SDA_M1/EBC_GDSP/CAN2_RX_M0/ISP_FLASH_TRIGIN/VOP_BT656_CLK_M1/GPIO4_B4_d |

I2C seriel port 2 |

1,8V |

I/O NED |

|

113 |

MIPI_CAM1_PDN_L_GPIO3_D3 |

LCDC_D1/VOP_BT656_D1_M0/SPI0_MOSI_M1/PCIE20_WAKEn_M1/I2S1_SCLK_TX_M2/GPIO2_D1_d |

Kamera1 slukker |

3,3V |

I/O NED |

|

114 |

MIPI_CAM1_RST_L_GPIO3_D2 |

LCDC_D0/VOP_BT656_D0_M0/SPI0_MISO_M1/PCIE20_CLKREQn_M1/I2S1_MCLK_M2/GPIO2_D0_d |

Kamera1 nulstillet |

3,3V |

I/O NED |

|

115 |

MIPI_CAM0_RST_L_GPIO3_D4 |

LCDC_D2/VOP_BT656_D2_M0/SPI0_CS0_M1/PCIE30X1_CLKREQn_M1/I2S1_LRCK_TX_M2/GPIO2_D2_d |

Kamera0 nulstillet |

3,3V |

I/O NED |

|

116 |

MIPI_CAM0_PDN_L_GPIO3_D5 |

LCDC_D3/VOP_BT656_D3_M0/SPI0_CLK_M1/PCIE30X1_WAKEn_M1/I2S1_SDI0_M2/GPIO2_D3_d |

Kamera0 slukker |

3,3V |

I/O NED |

|

117 |

USB2_HOST2_DM |

USB2_HOST2_DM |

USB2_HOST2_DM |

3,3V |

- |

|

118 |

USB2_HOST2_DP |

USB2_HOST2_DP |

USB2_HOST2_DP |

3,3V |

- |

|

119 |

USB2_HOST3_DM |

USB2_HOST3_DM |

USB2_HOST3_DM |

3,3V |

- |

|

120 |

USB2_HOST3_DP |

USB2_HOST3_DP |

USB2_HOST3_DP |

3,3V |

- |

|

121 |

REFCLK_OUT |

REFCLK_OUT/GPIO0_A0_d |

Urudgang til kamera |

3,3V |

I/O NED |

|

122 |

CIF_CLKOUT |

CIF_CLKOUT/EBC_GDCLK/PWM11_IR_M1/GPIO4_C0_d |

CIF ur ud |

1,8V |

I/O NED |

|

123 |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

1,8V |

- |

|

124 |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

1,8V |

- |

|

125 |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

1,8V |

- |

|

126 |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

1,8V |

- |

|

127 |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

1,8V |

- |

|

128 |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

1,8V |

- |

|

129 |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

1,8V |

- |

|

130 |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

1,8V |

- |

|

131 |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

1,8V |

- |

|

132 |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

1,8V |

- |

|

133 |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

1,8V |

- |

|

134 |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

1,8V |

- |

|

135 |

LCD1_PWREN_H_GPIO0_C5 |

PWM6/SPI0_MISO_M0/PCIE30X2_WAKEn_M0/GPIO0_C5_d |

LCD-strømaktivering |

3,3V |

I/O NED |

|

136 |

LCD1_BL_PWM5 |

PWM5/SPI0_CS1_M0/UART0_RTSn/GPIO0_C4_d |

LCD-baggrundsbelysning PWM |

3,3V |

I/O NED |

|

137 |

LCD1_BL_PWM4 |

PWM4/VOP_PWM_M0/PCIE30X1_PERSTn_M0/MCU_JTAG_TRSTn/GPIO0_C3_d |

LCD-baggrundsbelysning PWM |

3,3V |

I/O NED |

|

138 |

LCD0_PWREN_H_GPIO0_C7 |

HDMITX_CEC_M1/PWM0_M1/UART0_CTSn/GPIO0_C7_d |

LCD-strømaktivering |

3,3V |

I/O NED |

|

139 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

1,8V |

- |

|

140 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

1,8V |

- |

|

141 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

1,8V |

- |

|

142 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

1,8V |

- |

|

143 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

1,8V |

- |

|

144 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

1,8V |

- |

|

145 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

1,8V |

- |

|

146 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

1,8V |

- |

|

147 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

1,8V |

- |

|

148 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

1,8V |

- |

|

149 |

HDMI_TXCLKN_PORT |

HDMI_TX_CLKN |

HDMI_TX2CLKN_PORT og seriemodstand 2.2R |

1,8V |

- |

|

150 |

HDMI_TXCLKP_PORT |

HDMI_TX_CLKP |

HDMI_TXCLKP_PORT og seriemodstand 2.2R |

1,8V |

- |

|

151 |

HDMI_TX0N_PORT |

HDMI_TX_D0N |

HDMI_TX0N_PORT, og seriemodstand 2.2R |

1,8V |

- |

|

152 |

HDMI_TX0P_PORT |

HDMI_TX_D0P |

HDMI_TX0P_PORT, og seriemodstand 2.2R |

1,8V |

- |

|

153 |

HDMI_TX1N_PORT |

HDMI_TX_D1N |

HDMI_TX1N_PORT, og seriemodstand 2.2R |

1,8V |

- |

|

154 |

HDMI_TX1P_PORT |

HDMI_TX_D1P |

HDMI_TX1P_PORT, og seriemodstand 2.2R |

1,8V |

- |

|

155 |

HDMI_TX2N_PORT |

HDMI_TX_D2N |

HDMI_TX2N_PORT, og seriemodstand 2.2R |

1,8V |

- |

|

156 |

HDMI_TX2P_PORT |

HDMI_TX_D2P |

HDMI_TX2P_PORT og seriemodstand 2.2R |

1,8V |

- |

|

157 |

HDMITX_SCL |

HDMITX_SCL/I2C5_SCL_M1/GPIO4_C7_u |

I2C seriel port til HDMI |

3,3V |

I/O OP |

|

158 |

HDMITC_SDA |

HDMITX_SDA/I2C5_SDA_M1/GPIO4_D0_u |

I2C seriel port til HDMI |

3,3V |

I/O OP |

|

159 |

HDMITX_CEC_M0 |

HDMITX_CEC_M0/SPI3_CS1_M1/GPIO4_D1_u |

HDMITX_CEC |

3,3V |

I/O OP |

|

160 |

HDMI_TX_HPDIN |

HDMI_TX_HPDIN |

HDMI_TX hot plug |

1,8V |

- |

|

161 |

PCIE30X2_CLKREQN_M1 |

LCDC_D4/VOP_BT656_D4_M0/SPI2_CS1_M1/PCIE30X2_CLKREQn_M1/I2S1_SDI1_M2/GPIO2_D4_d |

PCIE30X2_CLKREQn |

3.3 |

I/O NED |

|

162 |

PCIE30X2_WAKEN_M1 |

LCDC_D5/VOP_BT656_D5_M0/SPI2_CS0_M1/PCIE30X2_WAKEn_M1/I2S1_SDI2_M2/GPIO2_D5_d |

PCIE30X2_WAKEn |

3,3V |

I/O NED |

|

163 |

PCIE30X2_PERSTN_M1 |

LCDC_D6/VOP_BT656_D6_M0/SPI2_MOSI_M1/PCIE30X2_PERSTn_M1/I2S1_SDI3_M2/GPIO2_D6_d |

PCIE30X2 nulstillet |

3,3V |

I/O NED |

|

164 |

PCIE30X2_PRSNT_L_GPIO2_D7 |

LCDC_D7/VOP_BT656_D7_M0/SPI2_MISO_M1/UART8_TX_M1/I2S1_SDO0_M2/GPIO2_D7_d |

PCIE30X2 wake vært |

3,3V |

I/O NED |

|

165 |

PCIE_PWREN_H_GPIO0_D4 |

GPIO0_D4_d |

PCIE-strømaktivering |

1,8V |

I/O NED |

|

166 |

PCIE30_RX1N |

PCIE30_RX1N |

PCIE30_RX1N |

1,8V |

- |

|

167 |

PCIE30_RX1P |

PCIE30_RX1P |

PCIE30_RX1P |

1,8V |

- |

|

168 |

PCIE30_RX0N |

PCIE30_RX0N |

PCIE30_RX0N |

1,8V |

- |

|

169 |

PCIE30_RX0P |

PCIE30_RX0P |

PCIE30_RX0P |

1,8V |

- |

|

170 |

PCIE30_TX1N |

PCIE30_TX1N |

PCIE30_TX1N |

1,8V |

- |

|

171 |

PCIE30_TX1P |

PCIE30_TX1P |

PCIE30_TX1P |

1,8V |

- |

|

172 |

PCIE30_TX0N |

PCIE30_TX0N |

PCIE30_TX0N |

1,8V |

- |

|

173 |

PCIE30_TX0P |

PCIE30_TX0P |

PCIE30_TX0P |

1,8V |

- |

|

174 |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

1,8V |

- |

|

175 |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

1,8V |

- |

|

176 |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

1,8V |

- |

|

177 |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

1,8V |

- |

|

178 |

SATA2_RXN |

PCIE20_RXN/SATA2_RXN/QSGMII_RXN_M1 |

SATA2_RXN |

1,8V |

- |

|

179 |

SATA2_RXP |

PCIE20_RXP/SATA2_RXP/QSGMII_RXP_M1 |

SATA2_RXP |

1,8V |

- |

|

180 |

SATA2_TXN |

PCIE20_TXN/SATA2_TXN/QSGMII_TXN_M1 |

SATA2_TXN |

1,8V |

- |

|

181 |

SATA2_TXP |

PCIE20_TXP/SATA2_TXP/QSGMII_TXP_M1 |

SATA2_TXP |

1,8V |

- |

|

182 |

SATA2_ACT_LED |

EDP_HPDIN_M0/SPDIF_TX_M2/SATA2_ACT_LED/PCIE30X2_PERSTn_M2/I2S3_LRCK_M1/GPIO4_C4_d |

SATA aktiv angiver |

3,3V |

I/O NED |

|

183 |

USB3_HOST1_SSTXP |

USB3_HOST1_SSTXP/SATA1_TXP/QSGMII_TXP_M0 |

USB3_HOST1_SSTXP |

1,8V |

- |

|

184 |

USB3_HOST1_SSTXN |

USB3_HOST1_SSTXN/SATA1_TXN/QSGMII_TXN_M0 |

USB3_HOST1_SSTXN |

1,8V |

- |

|

185 |

USB3_HOST1_SSRXP |

USB3_HOST1_SSRXP/SATA1_RXP/QSGMII_RXP_M0 |

USB3_HOST1_SSRXP |

1,8V |

- |

|

186 |

USB3_HOST1_SSRXN |

USB3_HOST1_SSRXN/SATA1_RXN/QSGMII_RXN_M0 |

USB3_HOST1_SSRXN |

1,8V |

- |

|

187 |

USB3_HOST1_DM |

USB3_HOST1_DM |

USB3_HOST1_DM |

3,3V |

- |

|

188 |

USB3_HOST1_DP |

USB3_HOST1_DP |

USB3_HOST1_DP |

3,3V |

- |

|

189 |

USB3_OTG0_SSTXP |

USB3_OTG0_SSTXP/SATA0_TXP |

USB3_OTG0_SSTXP |

1,8V |

- |

|

190 |

USB3_OTG0_SSTXN |

USB3_OTG0_SSTXN/SATA0_TXN |

USB3_OTG0_SSTXN |

1,8V |

- |

|

191 |

USB3_OTG0_SSRXP |

USB3_OTG0_SSRXP/SATA0_RXP |

USB3_OTG0_SSRXP |

1,8V |

- |

|

192 |

USB3_OTG0_SSRXN |

USB3_OTG0_SSRXN/SATA0_RXN |

USB3_OTG0_SSRXN |

1,8V |

- |

|

193 |

USB3_OTG0_DM |

USB3_OTG0_DM |

USB3_OTG0_DM |

3,3V |

- |

|

194 |

USB3_OTG0_DP |

USB3_OTG0_DP |

USB3_OTG0_DP |

3,3V |

- |

|

195 |

USB3_OTG0_ID |

USB3_OTG0_ID |

USB3_OTG0_ID |

3,3V |

- |

|

196 |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUS detektering |

3,3V |

- |

|

197 |

USB_HOST_PWREN_H_GPIO0_A6 |

GPU_PWREN/SATA_CP_POD/PCIE30X2_CLKREQn_M0/GPIO0_A6_d |

USB-værtsstrømaktivering |

3,3V |

I/O NED |

|

198 |

USB_OTG_PWREN_H_GPIO0_A5 |

SDMMC0_PWREN/SATA_MP_SWITCH/PCIE20_CLKREQn_M0/GPIO0_A5_d |

USB OTG-strømaktivering |

3,3V |

I/O NED |

|

199 |

DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

1,8V |

- |

|

200 |

DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

1,8V |

- |

|

201 |

DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

1,8V |

- |

|

202 |

DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

1,8v |

- |

|

203 |

DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

1,8V |

- |

|

204 |

DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

1,8V |

- |

|

205 |

DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

1,8V |

- |

|

206 |

DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

1,8V |

- |

|

207 |

DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

1,8V |

- |

|

208 |

DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

1,8V |

- |

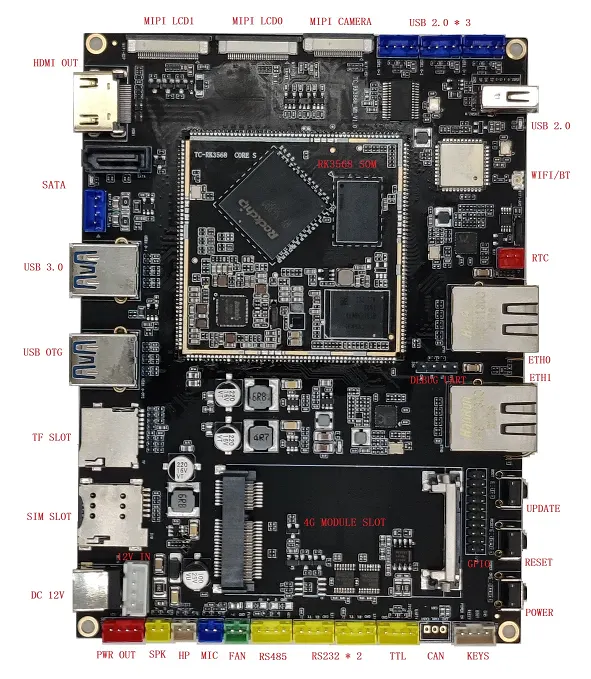

Kapitel 3. Udviklingsnævn

Størrelse

Størrelsen er 150mm*110mm, 4 lag, 1,6mm tykkelse.

Grænseflader Beskrivelse

|

Grænseflader Beskrivelse |

|

|

INGEN. |

Navn |

|

ã1ã |

DC 12V Indgang/4pin 2,54mm 12V Indgang |

|

ã2ã |

4G-modul SIM-kortslot |

|

ã3ã |

TF kortslot |

|

ã4ã |

USB OTG |

|

ã5ã |

USB3.0 VÆRT |

|

ã6ã |

SATA data |

|

ã7ã |

HDMI udgang |

|

ã8ã |

MIPI LCD1 |

|

ã9ã |

MIPI LCD0 |

|

ã10ã |

MIPI kamera |

|

ã11ã |

USB 2.0 * 3 |

|

ã12ã |

USB 2.0 TypeA |

|

ã13ã |

WIFI/BT(AP6335) |

|

ã14ã |

RTC |

|

ã15ã |

ETH0 |

|

ã16ã |

ETH1 |

|

ã17ã |

Opdater nøgle |

|

ã18ã |

Nulstil nøgle |

|

ã19ã |

Power-tast |

|

ã20ã |

Nøgler (4-benet 2,0 mm) |

|

ã21ã |

CAN (3 ben 2,0 mm) |

|

ã22ã |

Uart TTL (4-pin 2,0 mm) |

|

ã23ã |

RS232 * 2 (4-benet 2,0 mm) |

|

ã24ã |

RS485 (4-benet 2,0 mm) |

|

ã25ã |

VENTILATOR (2 ben 2,0 mm) |

|

ã26ã |

MIC (2 ben 2,0 mm) |

|

ã27ã |

HP (2 ben 2,0 mm) |

|

ã28ã |

SPK (2 ben 2,0 mm) |

|

ã29ã |

Strømudgang (4-benet 2,0 mm) |

|

ã30ã |

Debug Uart (4-pin 2,0 mm) |

|

ã31ã |

GPIO(2*10pin 2,0mm) |

|

ã32ã |

4G-modulslot (PCIE-port) |

|

ã33ã |

RK3568 SOM |

Kortet bruger 12V DC strømforsyning, der forbindes med DC 12V Input stik eller 4pin 2,54mm 12V Input stik.

Detaljer om andre grænseflader kan henvise til det skematiske diagram og layoutet af udviklingstavlen.

Kapitel 4. Hardwaredesign

Design reference

Tag TC-RK3568 Development Board som hardwareplatform, du kan henvise til Power design, USB design, PCIE Port design, MIPI display design, Audio design, Ethernet design, Camera design, og så videre. Disse er åbne for kunder, kan henvise til vores carrier board design.

Kapitel 5. Softwaredesign

TC-RK3568 udvikler platform understøtter Android11, Linux Buildroot, Ubuntu og Debian System OS, kildekoder er åbne. Du kan læse referencerne, såsom Thinkcore TC-RK3568-systemets brugermanual.